可控硅触发器系列

时间: 2026-03-22 13:03:44 | 作者: 可控硅触发器系列

产品详情

触发器是一种边缘触发触发器,意味着只需当时钟脉冲施加到其时钟输入时,它的输出才会改动。

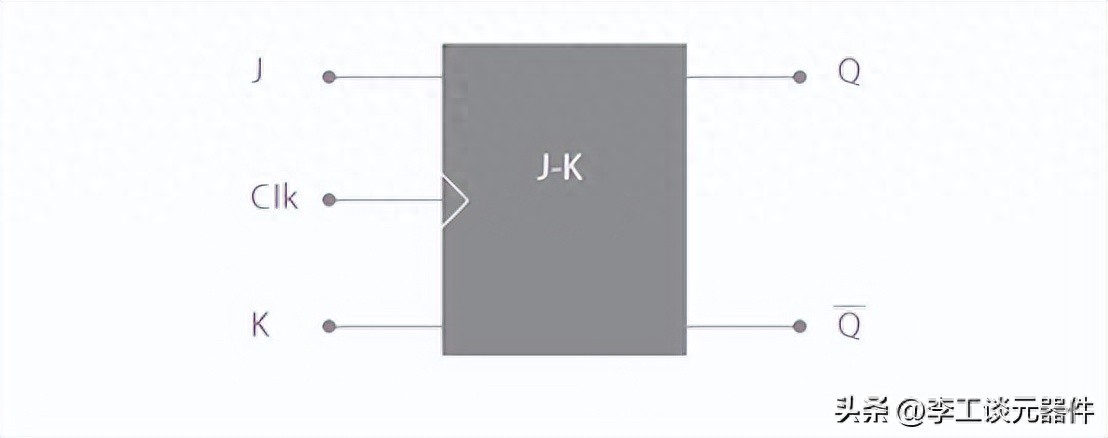

JK触发器由两个输入 J(置位)和 K(复位)、一个时钟输入以及两个表明为 Q 和 Q 的输出组成。

时钟输入用于触发触发器并改动其状况。Q是JK触发器的主输出,Q是输出Q的补码。

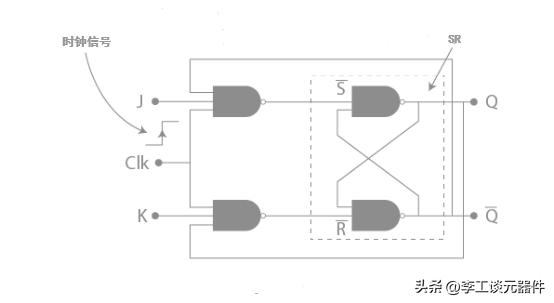

JK触发器的内部结构可以用 NAND 门锁存器来解说。与非门是一种逻辑门,发生的输出是其输入的逻辑与的补码,JK触发器由两个与非门构成,如下图所示:

输入 J 和 K 连接到榜首与非门的输入,而榜首与非门的输出连接到第二与非门的输入。第二个与非门的输出连接到榜首个与非门的输入,也构成反应回路(这便是它们被称为时序电路的原因)。输入时钟连接到两个与非门,其信号决议触发器的输出何时改动。

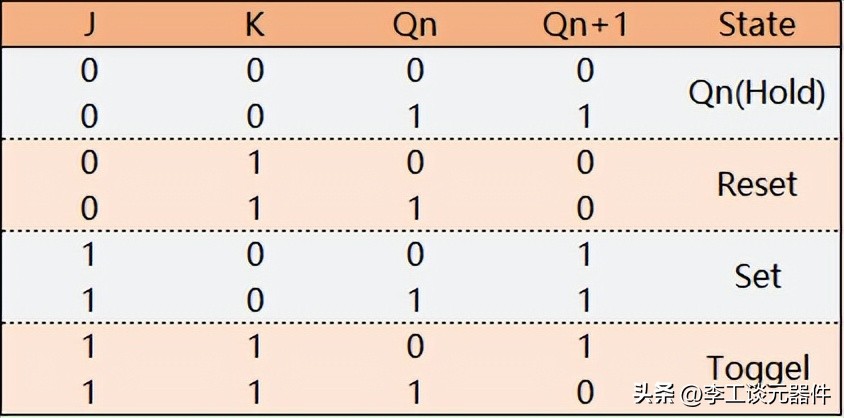

JK触发器真值表有坚持状况、复位状况、置位状况和切换状况。因为这是SR触发器的细化,因而将SR触发器的真值表细化为IK触发器的真值表。

JK触发器的真值表有两个输入,J和K,Q n表明当时状况, Q n+1表明下一个状况,如下表所示:

如下:在上面的真值表中,Q(n)代表触发器在n时间的输出,而Q(n+1)代表其在n+1时间的输出。

。特征表有输入 J 和 K,Qn 和 Q n+1表明当时状况,表明特征表中的下一个状况,如下所示:

上述特性表中具有坚持状况、复位状况、置位状况和切换状况的 JK 触发器的特性方程运用三变量 k-map 如下所示。

通过两个 NAND 门的传达推迟时间 t pd后,输出将切换至 Q n = 1。因为这是对输入的反应,因而在另一次推迟 t pd (FF)后,输出将切换回 Q n = 0 。

只需低时钟脉冲宽度善于触发器传达推迟(t pd),这样的一种状况就会继续下去。

相关推荐